- TI introduces newest member of TMS320C66x DSP generation, the TMS320C6671 DSP, industry’s fastest fixed-and floating-point single core device, easing developers’ transition to multicore with strategic design approach

- TI drives performance and efficiency to record levels for communication-centric applications with new features and enhancements to TMS320C6670 radio SoC

- Developers gain total scalability in product design with TI’s pin and software compatible C66x DSP generation

Continuing to unleash higher performance levels and more innovations in the multicore space, Texas Instruments Incorporated today introduced the newest digital signal processor (DSP) in the TMS320C66x DSP generation, the TMS320C6671 device, as well as enhancements to its TMS320C6670 radio System-on-Chip (SoC). Based on TI’s KeyStone multicore architecture, the C6671 DSP, the industry’s fastest and highest performing fixed-and floating-point single core device, offers a compelling choice for developers wanting to ease into the world of multicore. At the same time, TI’s enhanced C6670 radio SoC delivers double the power/performance improvement over existing SoC solutions for communications-centric applications.

Features

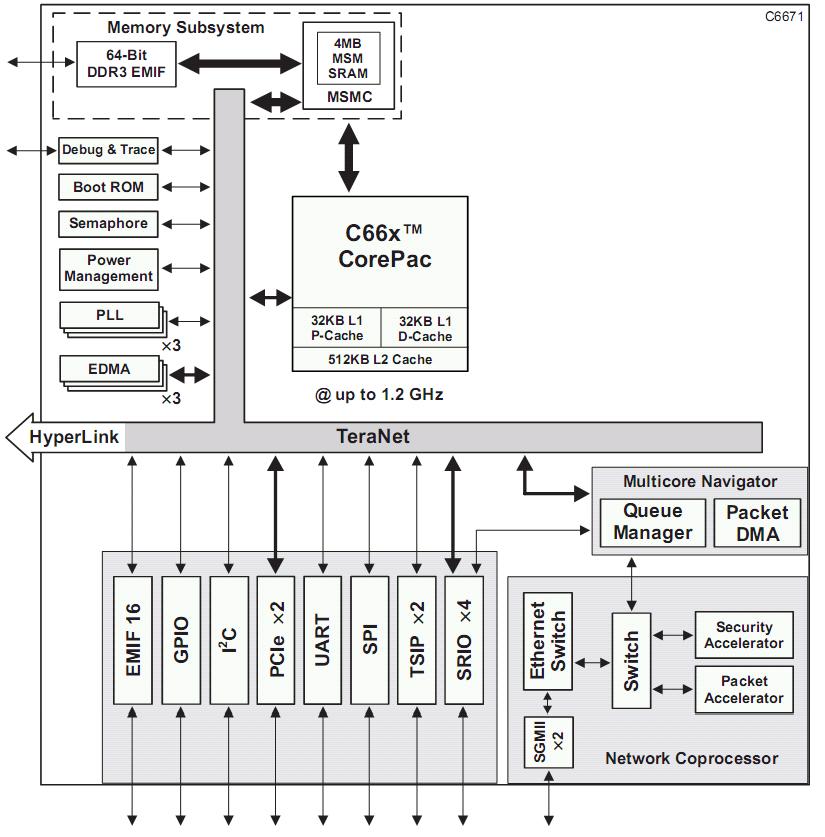

- One TMS320C66x DSP Core Subsystems at 1.00 GHz and 1.25GHz

- 40 GMAC/20 GFLOP @ 1.2GHz

- 32KB L1P, 32KB L1D, 512KB L2

- 1 MB Shared L2

- Multicore Navigator and TeraNet Switch Fabric - 2 Tb

- Network Coprocessors- Packet Accelerator, Security Accelerator

- Four Lanes of SRIO 2.1 - 5 Gbaud Per Lane Full Duplex

- Two Lanes PCIe Gen2 - 5 Gbaud Per Lane Full Duplex

- HyperLink - 50Gbaud Operation, Full Duplex

- Ethernet MAC Subsystem - Two SGMII Ports w/ 10/100/1000 Mbps operation

- 64-Bit DDR3 Interface (DDR3-1600) - 8 GByte Addressable Memory Space

- 16-Bit EMIF - Async SRAM, NAND and NOR Flash Support

- Two Telecom Serial Ports (TSIP) - 2/4/8 Lanes at 32.768/16.384/8.192

- UART Interface

- I2C Interface

- 16 GPIO Pins

- SPI Interface

- Sixteen 64-Bit Timers

- Three On-Chip PLLsv

"TI is taking multicore to a whole new level by delivering solutions at higher performance levels and in less time than competing solutions,” said Ramesh Kumar, business manager, multicore and media infrastructure, Texas Instruments. “For developers of high-performance applications wanting a feel for multicore performance but who are used to designing with single core devices, our C6671 DSP offers a true ‘stepping stone’ into multicore. And for developers needing more performance in communications-centric applications, our C6670 radio SoC offers enhancements that cannot be seen anywhere else.”

Easing into multicore with TI’s C6671 DSP

TI’s C6671 DSP, the first 1.25 GHz single core member of the C66x DSP generation, utilizes a strategic design approach that familiarizes developers with multicore devices without needing the expertise of working with such a device. Customers designing with the C6671 DSP will benefit from TI’s benchmark-busting multicore features including high-performance, increased number of peripherals and memory per core, and fixed-and floating-point performance on a single device.

Using TI’s C6671 DSP, developers can test out whether or not multicore devices suit their needs and explore options for migrating their designs to other processors in TI’s C66x DSP portfolio if more performance is needed down the road. By offering pin and software compatible platforms across TI’s TMS320C6672, TMS320C6674 and TMS320C6678 multicore DSPs, customers can more easily design integrated, power and cost-efficient products for high-performance markets such as mission critical, public safety and defense, medical and high-end imaging, test and automation, high-performance computing and core networking.

Enabling communications-centric applications with TI’s C6670 radio SoC

TI’s enhanced C6670 radio SoC is a 1.2 GHz four core device boasting improved accelerators for communications-centric applications including software defined radios (SDRs), public safety and emerging broadband radio systems. The added enhancements to the C6670 radio SoC include a new multistandard Bit Rate Coprocessor (BCP) as well as other coprocessors that accelerate physical layer processing for LTE, WCDMA, TD-SCDMA and WiMAX, substantially increasing system capacity and performance with low latency. In addition, the well balanced programmable CPU cores and configurable accelerators enable software defined radios with a simplified programming model. The addition of improved accelerators enables developers to develop multistandard communications-centric solutions for the industry.

Earlier today, TI announced significant updates to its multicore software and tools, including a free multicore software development kit (MCSDK), Linux software, optimized libraries and support for the OpenMP programming model. TI’s software offerings simplify developers’ migration to multicore solutions and allow manufacturers to develop a wider portfolio of solutions at a lower cost, lower power, and in less time than with competing solutions.

TI’s KeyStone Multicore Architecture

Texas Instruments’ KeyStone multicore architecture is the platform for true multicore innovation, offering developers a robust portfolio of high performance, low-power multicore devices. Unleashing breakthrough performance, the Keystone architecture is the foundation upon which TI’s new TMS320C66x DSP generation was developed. KeyStone differs from any other multicore architecture as it has the capacity to provide full processing capability to every core in a multicore device. KeyStone-based devices are optimized for high performance markets including wireless base stations, mission critical, test and automation, medical imaging and high performance computing.