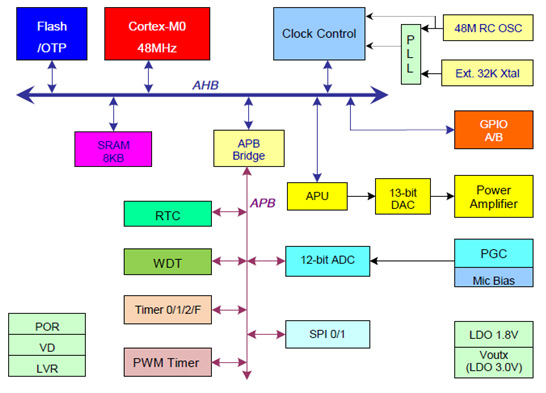

After the success of first M0-based NuVoice, Nuvoton Technology Corporation introduced the second NuVoice - N572F072. The N572F072 is the enhanced N572 series from N572F064/F065, the first Cortex-M0 based processor for voice applications. It runs up to 48MHz and equipped with 72KB flash and 8KB SRAM for high performance processing of audio and voice algorithms. Integrating rich analog peripherals, like pre-amplifier, ADC, DAC, hardware mixer, and PA, this chip saves a lot of system design effort and cost.

Key features:

- Core

- ARM Cortex-M0 core runs up to 48MHz

- Support low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 16 interrupt inputs, each with 4-level of priority

- 24-bit sysTick timer

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Flash EPROM Memory

- 72KB Flash EPROM (for N572F072)

- 64KB OTP and 8KB Flash or 72KB OTP (for N572P072)

- Support ISP for Flash update

- 512 bytes page erase for Flash

- Support 2-wire ICP update from ICE interface

- Security Lock preventing content in Flash access from external interface

- SRAM Memory

- 8KB embedded SRAM

- Clock Control

- Flexible selection for different applications

- Support PLL, up to 48MHz, for high performance system operation

- External 32KHz crystal input for RTC function and system clock

- Internal 48MHz RC oscillator

- GPIO

- Four I/O modes:

- Quasi bi-direction

- ‹Push-Pull output

- ‹Open-Drain output

- ‹Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- Four I/O modes:

- Timers

- 3 sets of the timer with 8-bit pre-scaler and 16-bit timer.

- Counter auto reload.

- IR carrier generator

- One fixed frequency timer

- PWM Timer

- One 16-bit timer and four 16-bit comparators

- Five clock selectors

- One 8-bit pre-scaler and one clock divider

- Two Dead-Zone generators

- Programmable duty control of output waveform

- Auto reload mode or one-shot pulse mode

- Capture function

- SPI

- Two sets of SPI device

- Master mode up to 24MHz (3.3V)

- Support master/slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 1 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- 2 slave/device select lines

- Two 32-bit buffers

- ADC

- 8-ch 12-bit with 320Ksps

- Single scan/single cycle scan/continuous scan

- 8 channels share 8 result registers

- Programmable channel scan sequence

- Threshold voltage detection

- Conversion start by S/W or an external pin

- Programmable gain control for sound record

- Internal microphone bias

- APU

- 13-bit DAC

- H/W mixer with 2 channel PCM inputs

- Embedded power amplifier

- 7-level volume control

- Voltage Detector, Built-in 1.8V LDO

- Packages:

- All Green package (RoHS)

- 7mm×7mm LQFP 64-pin or COB

To unfold the high performance M0 and high density of SRAM, advanced algorithms are designed, optimized, and tested in N572 chip. These algorithms include voice changer, low-bit rate compression, beat detection, pitch shift, and more under development. In addition to algorithms developed by Nuvoton, we also seek third parties for more interesting software to enrich the applications on N572.

With the NVIC in M0, the latency of interrupt and response time to external events is very short and predictable. Multiple algorithms can be run together smoothly and naturally.

The development tools are based on Keil MDK using C/C++ programming language. This is a robust and easy-to-use environment for development and debugging. Features in Keil MDK are compiler, debugger, and profiler. With the Nu-Link and evaluation board, the overall system, including HW and SW, can work seamlessly in the system testing and verification. With this full featured development environment and tools, users can design and build application software in an efficient way and get optimized code that can best realize customers’ idea on N572.