Cadence Design Systems, Inc. introduced Spectre XPS (eXtensive Partitioning Simulator), a high-performance FastSPICE simulator that enables faster and more comprehensive simulation for large, complex chip designs. The new simulator delivers ground-breaking partitioning technology that brings up to 10X faster throughput compared to competitive offerings, shortening simulation from weeks to days. Spectre XPS uniquely enables designers to accurately measure timing while including the impact of IR drop, making it ideal for advanced-node, low-power mobile designs, where high performance, accuracy and a greater capacity for post-layout verification are imperatives.

Chip design—driven by increasingly sophisticated applications and shrinking process geometries—continues to get more complex. At the same time, traditional FastSPICE technologies are no longer effective in meeting the verification challenges found at advanced nodes. Cadence’s new Spectre eXtensive Partitioning Simulator (XPS) fills a gap in simulation technology, providing capabilities that address increasing parasitics, low-power circuit structures, variation, and other advanced-node challenges.

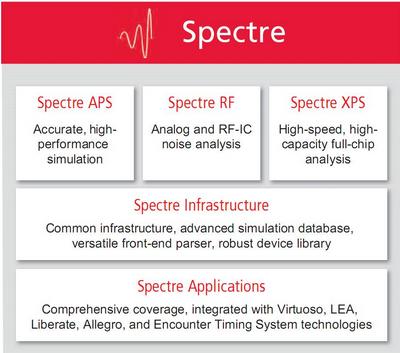

Built on the leading Cadence Spectre simulation platform, Spectre XPS allows the easy re-use of models, stimulus, analysis and overall methodology, thereby reducing support costs while improving time to production. The unified Spectre simulation platform spans SPICE, advanced SPICE, RF and FastSPICE, enabling easy transition across analysis and flows; Spectre XPS integrates into the Virtuoso Analog Design Environment for mixed-signal design, and into the Liberate MX memory characterization tool for SRAM memory characterization.The faster throughput of Spectre XPS lets design teams conduct more thorough and accurate simulations for large memory-intensive designs, as well as low-power architectures that require greater visibility into parasitics. In addition to improvements in throughput, the new simulator requires two to three times less system memory than competitive offerings, improving compute resources utilization.

Features/Benefits

- New FastSPICE algorithm and unique partitioning technology address parasitics, low-power circuit structures, variations, and other challenges that emerge at advanced nodes

- Supports higher capacity, with up to 10X faster simulation throughput with up to 3X less system memory

- Delivers highly accurate timing analysis—particularly critical for advanced-node, low-power mobile applications

- Shortens simulation time from weeks to just days

- Provides event-driven, multi-rate simulation

- Features advanced model reduction technology

- Offers advanced static and dynamic checking

- Provides full macro simulations for variation

- Integrates with Spectre Circuit Simulator platform, enabling reuse of models, methodologies, and process design kits (PDKs) for reduced support costs and faster time to production

- Integrates with Cadence Virtuoso Analog Design Environment for mixed-signal design and with Cadence Virtuoso Liberate MX memory characterization tool for SRAM memory characterization

“With the order of magnitude performance improvement of Spectre XPS, we are able to meet required turnaround time and quality-of-results goals,” said Suravi Bhowmik, manager, MCU Backplane, Embedded Processing, Texas Instruments Incorporated. “Our production rollout of Spectre XPS has enabled us to deliver accurate leakage and dynamic power results on complex low-power designs.”

“As designs continue to grow in complexity and size, new simulation technologies are needed to address such issues as the timing impact of IR drop and power gating,” said Tom Beckley, senior vice president, Custom IC and PCB Group. “The Spectre XPS FastSPICE simulator addresses these new challenges through next generation algorithms that deliver the simulation accuracy and performance required to reduce the risks of developing cutting-edge differentiated designs.”