New Family of 8-bit ADCs Delivers 6 GSPS Data Capture at Only 3.6 W

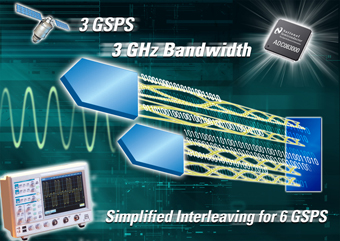

A new 8-bit, ultra-high-speed analog-to-digital converter (ADC) family from National Semiconductor Corporation sets a new performance standard for sampling speed, delivering 6 giga-sample per second (GSPS) data capture at 3.6 W. The single ADC083000 ADC operates at 3 GSPS and can be interleaved in a pair for 6 GSPS data capture without any additional clock adjustment circuitry. A full-power input bandwidth of 3 GHz, superior dynamic performance and low power consumption of 1.8 W complete the list of best-in-class features.

In addition, National is introducing two other ADCs, the ADC082500, capable of sampling speeds up to 2.5 GSPS, and the ADC08B3000. The ADC083000 and ADC082500 are well-suited for communications and test and measurement applications. The ADC08B3000, which combines 3 GSPS sampling and a programmable 4K byte memory buffer, is ideal for ranging applications such as RADAR and LIDAR (light detecting and ranging), where the data is captured in bursts and transferred at lower, more manageable data rates.

These ADCs feature a unique folding/interpolating architecture. Folding reduces the number of comparators, and interpolation greatly reduces the number of front-end amplifiers required, saving power and reducing the load on the input signal. National fabricates the ADC family on its proprietary, analog-optimized 0.18-micron CMOS process technology in its state-of-the-art South Portland, Maine facility.

About the ADCs

The ADC083000 can digitize an input signal into 8 bits at sampling speeds up to 3 GSPS. It provides a wide, 3GHz, full-power bandwidth, allowing for sampling of wideband signals even in the second Nyquist band. It has an adjustable sampling clock phase that allows designers to interleave multiple ADCs on a board without using costly, external clock-adjustment circuits. The converter offers 1:4 de-multiplexed outputs standard for simplified data capture or a new 1:2 output mode for reduced pin count when interfacing with an application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA). Both of these output modes use low-voltage differential signaling (LVDS). The ADC083000 also has test patterns on the outputs for easier system design and test. A three-wire serial bus controls these features, as well as on-chip functionality, and gain and offset fine-tuning for the input.

The ADC083000 typically achieves 7.0 effective number of bits (ENOB), 44 dB signal-to-noise ratio (SNR) and 54 dB spurious free dynamic range (SFDR) when sampling a 750 MHz input at 3 GSPS. The ADC082500 is a 2.5 GSPS version of the ADC083000.

The ADC08B3000's integrated memory buffer reduces system cost and design complexity, providing National’s customers with an efficient architecture for their systems. The ADC08B3000 samples one input at speeds up to 3 GSPS and stores the data in a 4K byte first in, first out (FIFO) memory buffer. One or two 8-bit CMOS output buses then transfer data from the FIFO out of the ADC to the processor at slower rates of up to 400 Megabytes per second. The ADC08B3000 is an innovative systems approach to data acquisition for applications where signal pulses need to be captured at giga-sample speeds while processed at much slower rates. The ADC08B3000 has the same performance specifications as the ADC083000.

Pricing and Availability

All three ADCs will be available in January 2007. Samples are available now. The ADC083000 is priced at $523 in 1,000-unit quantities.