STMicroelectronics today revealed the new architecture that will be the backbone for the new members of its popular SPEAr (Structured Processor Enhanced Architecture) family of embedded microprocessors, targeting high-performance connectivity and embedded applications.

Leveraging its experience of the production-proven SPEAr300 and SPEAr600 lines, the new SPEAr1300 product line couples powerful dual ARM Cortex-A9 processors with a DDR3 memory interface and is manufactured in ST’s low-power 55nm HCMOS (high-speed CMOS) process technology. The dual ARM Cortex-A9 processors support fully symmetrical operation, at speeds up to 600MHz/core for 3000 DMIPS equivalent.

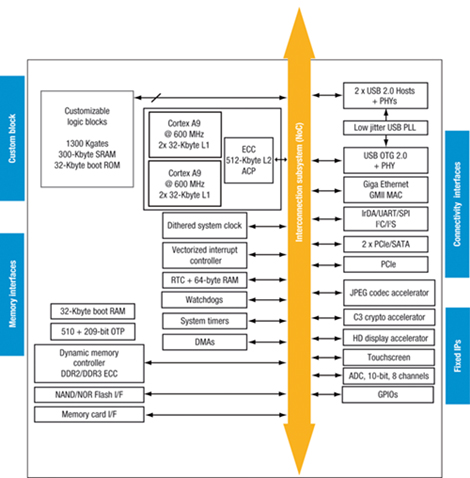

The SPEAr1300 makes use of ST’s innovative Network-on-Chip technology for internal peripheral interconnect, assuring support for multiple different traffic profiles, while maximizing data throughput in the most cost-effective and power-efficient way. Initial sampling has already started to early adopters.

The new architecture offers industry-leading performance in terms of DMIPS/MHz and power consumption/DMIPS ratios, in addition to cost efficiency and customizability advantages. The availability of integrated DDR3 memory controller and a full set of connectivity peripherals like PCIe, SATA, USB and Ethernet, among other features, make the SPEAr1300 the ideal choice for high-performance applications including networking, thin client, videoconferencing, NAS (Network-Attached Storage), computer peripherals, and factory automation.

“This new architecture for the SPEAr family builds upon the unrivalled low power and multiprocessing capabilities of the ARM Cortex-A9 processor core” said Loris Valenti, General Manager of ST’s Computer Systems SoC Division. “Upcoming SPEAr embedded microprocessors will deliver an unprecedented combination of processing performance, memory throughput, flexibility and low power for next-generation connectivity appliances.”

Key features of the new SPEAr1300 architecture include:

- Dual ARM Cortex-A9 cores, running at 600MHz for 3000 DMIPS equivalent

- 64-bit AXI (AMBA3) bus Network-on-Chip technology

- DRAM and L2 cache with Error Correction Code (ECC)

- 533MHz 32-bit DDR3 memory controllers with ECC; 16-bit DDR2 also supported

- Accelerator coherence port

- Gigabit Ethernet

- PCIe 2.0 supporting 5 GT/s (Gigatransfers/second)

- SATA II 3 Gbit/s

- USB 2.0

- 256-bit key hardware encryption/decryption

- 1.3 million gates of configurable logic

Embedded microprocessors from the new SPEAr1300 product line will be announced over the next few months, expanding ST’s SPEAr family and providing an extensive choice for leading customers.