Christoph Hammerschmidt

Renesas has added a coprocessor to its V850 architecture that brings the V850 microprocessor performance in signal processing applications on par with available dedicated high-end DSPs. The approach to integrate such a coprocessor on chip offers a number of advantages. With the development, Renesas plans to meet demand for high computing power in real-time applications such as factory automation and automotive engine control.

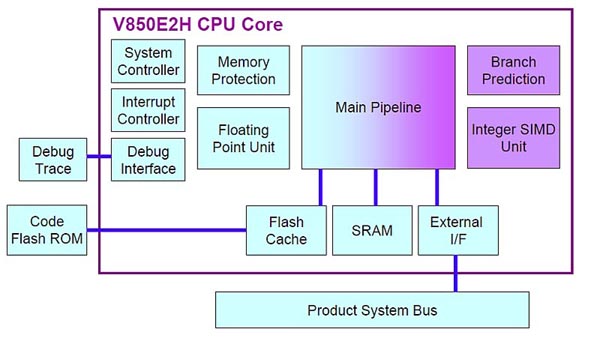

Renesas design engineers have added a coprocessor for the V850 microprocessor capable of processing single-instruction multiple-data (SIMD) operations; according to the company, four units of data can be executed by a single instruction. Besides the 64-bit SIMD registers, the coprocessor also is equipped with a dedicated pipeline for executing signal processing extended instructions.

In addition, the new architecture is equipped with a high-speed branch predictor which optimizes the execution of loop instructions. This add-on speeds up even programs that do not involve signal processing by some 10 percent.

These two features are the basic ingredients for Renesas' newly developed V850E2v4 architecture. The first CPU core based on this architecture is the V850E2H.

The architecture does not only speed program execution but also program development. Since there is no need for an external DSP, both the control program and the signal processing program can be designed and tested on a single program development environment - as opposed to the earlier approach where DSP and control programs are developed and tested separately; final software integration and testing can be omitted.

In applications where the new coprocessor can play on its strength, the program code size can be reduced significantly; at the same time, performance gain is spectacular. Renesas describes a 16-bit 128-point fast Fourier transformation algorithm which performed almost 12 times faster on the new architecture in comparison to the same function written in C and running on an earlier CPU core. At the same time, the code size shrunk to one-third, Renesas claims.

At the same time, the V850E2H core provides compatibility with the basic instruction set of the earlier V850E2M CPU at the object level. The IEEE 754 compliant floating-point arithmetic unit integrated into the V850E2M core can be integrated with the V850E2H core as well.

Offering both excellent control and signal processing performance, Renesas believes that the he V850E2H core will be a technology that will contribute to the development of programs for control systems requiring sophisticated analysis algorithms, such as vibration damping systems for Factory automation equipment and automotive control units such as knocking sensors that monitor automobile radar and engine fuel efficiency. Utilizing the new V850E2H core, the company plans to offer new MCU solutions to customers. No data as to the availability were provided.