Two new dual-channel galvanically-isolated gate drivers for IGBTs and silicon-carbide (SiC) MOSFETs from STMicroelectronics save space and ease circuit design in high-voltage power-conversion and industrial applications.

The STGAP2HD for IGBTs and STGAP2SICD for SiC MOSFETs leverage ST’s latest galvanic-isolation technology to provide 6 kV transient-voltage capability in a SO-36W wide-body package. In addition, ±100 V/ns dv/dt transient immunity prevents spurious turn-on in electrically noisy operating conditions. The devices can deliver a powerful gate-control signal of up to 4 A, with dual output pins for extra flexibility in gate driving, allowing independent adjustment of turn-on and turn-off times. The active Miller clamp prevents gate spikes during fast commutation in half-bridge topologies.

Circuit protection features include thermal protection, a watchdog for safe operation, and Under-Voltage Lockout (UVLO) per channel to prevent starting-up in a dangerous low-efficiency mode. The STGAP2SICD has a raised UVLO threshold voltage optimized for the needs of SiC MOSFETs.

|

| The STGAP2SiCD block diagram. |

Each device has an iLOCK pin for turning on both channels simultaneously in dual low-side and asymmetrical half-bridge applications. There is also interlocking to prevent shoot-through currents in conventional half-bridge circuits. Both drivers are rated for voltages up to 1200 V on the high-voltage rail and have input-to-output propagation time of 75 ns with high PWM accuracy.

With dedicated shutdown and brake pins, and a standby pin for power saving, ST’s new dual-channel galvanically-isolated gate drivers target applications including power supplies, drives, inverters, welders, and chargers. In addition, input pins compatible with TTL and CMOS logic down to 3.3 V simplify connection to a host microcontroller or DSP.

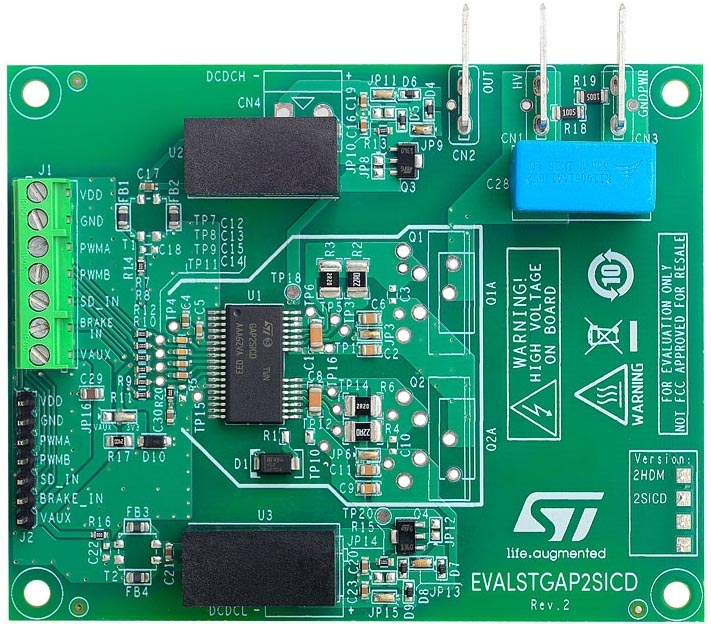

Both the STGAP2HD and STGAP2SICD are in production now and are priced from $1.84 for orders of 1000 pieces. The EVALSTGAP2HDM and EVALSTGAP2SICD demonstration boards are also available, allowing rapid evaluation of the drivers’ features when driving a half-bridge power stage.

|

| The EVALSTGAP2SICD demonstration board. |