Part 1 - Schematic

Firmware

Firmware was written in VHDL. Producer of the CPLD provides free development tools. For further informations check Xilinx website ISE WebPACK, ModelSim XE.

Although used FPGA XC95288XL is the biggest from the CPLD XL family, it is still not big enough to implement all logic and therefore several versions of firmware exist.

Currently exist following types of firmware:

Timeanalysis (1.x)

Most commonly used mode when sample is taken upon every clock pulse. In this mode 32 channels can be simultaneously sampled.

Documentation is included in the firmware release.

Stateanalysis (2.x)

In this mode memory data bus is divided into two halves. Lower-half of the memory bus (bits 0 to 15) is used for storing samples and upper half (bits 16 to 31) for timestamps. Samples are stored only in the case of difference with previous sample and timestamp then determines number of clocks from previous data change. This provides some sort of RLE compression and allows to extend time of measurement for slow changing signals. Disadvantage is limitation of simultaneously sampled channels to 16.

LED tester

LED tester is a simple firmware created in order to quickly test the functionality of miniLA hardware. It just implements 26 bits wide counter with its outputs driving status LEDs. Having CPLD programmed you should see LEDs blinking (bit 0 is connected to D5, bit 10 to D4 and bit 25 to D3).

CPLD programming:

Prior to use, the CPLD has to be programmed with appropriate firmware. This text describes programming using program iMPACT (part of the ISE WebPACK) and Xilinx LPT JTAG programmer (schematic).

- Connect TDI, TDO, TMS, TCK, VCC and GND between miniLA and programmer. Power up the miniLA.

- Start program iMPACT (Start -> Programs -> Xilinx ISE -> Accessories -> iMPACT)

- Choose Configure Devices, click NEXT

- Choose Boundary-Scan mode, click NEXT

- Choose Automatically connect to cable ..., click NEXT

- Now your programmer gets detected and picture of chip will show. Right click on the chip, choose Assign New Configuration File, browse to the *.jed file a click Open

- Right click on the chip, choose Program.... In following window only options Erase Before Programming and Verify should be selected. Click OK.

- CPLD will be programmed.

Software

|

Application

|

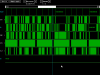

Application Window

|

Description

|

|

wx miniLA

|

|

Type: GUI OS: Linux, Win, Other Version: 0.7 Latest supported firmware: 1.7 Description: Fully multiplatform software, built with wxWidgets, and compatible with Code::Blocks IDE. |

|

minila win 0.x

|

|

minila_win_0.X Type: GUI OS: Win Version: 0.6.3 Latest supported firmware: 1.7, 2.2 Description: Complete program including communication with miniLA, waveform/text viewer, full triggering support, declaration of buses, protocol decoders (RS-232, I2C, SPI, PWM) and more. Supports LPT and USB interface. |

|

minila dos GUI

|

|

Type: viewer OS: DOS Version: 0.9 Description: DOS program for displaying of sampled data. Reads binary file, supports own definitions of signals and buses. |

|

Utilities

|

||

|

Utilities

|

|

OS: Win/DOS, Linux Version: 0.2 Description: Set of various utilities. Package currently contains standalone BIN to VCD converter and decoders of RS-232, I2C and SPI protocol. |

|

Various SW created but no longer in development.

|

||

|

minila win 1.X

|

|

Type: GUI OS: Win Version: 1.5.5 Latest supported firmware: 1.5.3 (limited) Description: This program originated from early-version of minila_win (ver 0.1) with an idea of program that would widely based on plugins. |

|

minila linux

|

|

Type: grabber OS: Linux Version: 0.3 Latest supported firmware: 1.6, 2.1 Description: Linux command line utility. It supports full functionality of miniLA. Output is in binary file or in VCD file (own definitions of signals and buses supported). Can be run under root or ordinary user. LPT port supported only. |

|

test win

|

|

Type: grabber OS: Win Version: 1.1.1 Latest supported firmware: 1.6, 2.1 Description: Very simple Delphi program developed for debug of communication between PC and miniLA via LPT port. For correct functionality on WinNT systems, driver allowing direct access to IO ports is necessary (GiveIO, UserPort etc.). |

|

List of programs not written by miniLA group, but which can be also used to display sampled data.

|

||

|

gtkWave

|

|

|

Downloads

Firmware - download

Software - download

Content of the EEPROM (MPROG template) - download

Parallel Download Cable III for Xilinx CPLD (Schematic and User Guide) - download

Communication protocol (Timeanalysis 1.x) - download

Communication protocol (Stateanalysis 2.x) - download