Application Note AN-1254

December 2013

David Brandon, Scott Shoaf

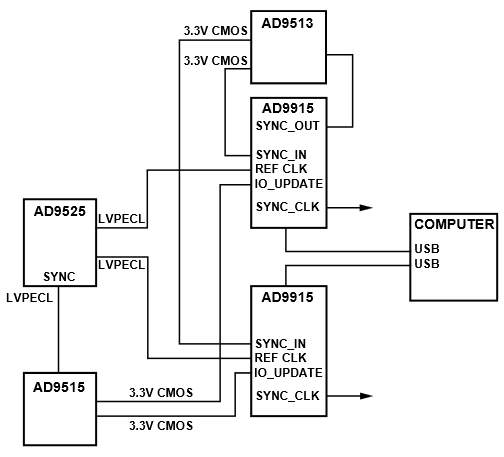

Various applications require the generation of two or more sinusoidal or square wave signals with a known phase relationship between them. The AD9915 DDS IC from Analog Devices, Inc., is capable of providing such signals. This application note offers detailed instructions on how to synchronize two or more of these devices and considers possible sources of phase error.

For successful synchronization, the user must have control over the timing of the REF CLK, SYNC_CLK, and the IO_UPDATE to each device. The goal is to have all DDS devices operating on the same internal system clock count and not off by ±1 or more counts between devices. Therefore, the SYNC_CLK of each device must be aligned to one another and the IO_UPDATE of each device must be made synchronous to the SYNC_CLK. As a result, all output phase error uncertainty of ±1 or more system clock period(s) is eliminated.

Note that any output phase error due to output filtering mismatches, REF CLK skew, and other external sources typically manifests as a fixed source of error. However, the DDS provides programmable output phase adjust features that can null out fixed sources of phase error. This application note describes the basic requirements to synchronize multiple DDS parts. Successful synchronization starts with the distribution of the REF CLK signal.

![]() Download Application Note AN-1254 (164 Kb)

Download Application Note AN-1254 (164 Kb)

Related datasheets:

Concept Circuit