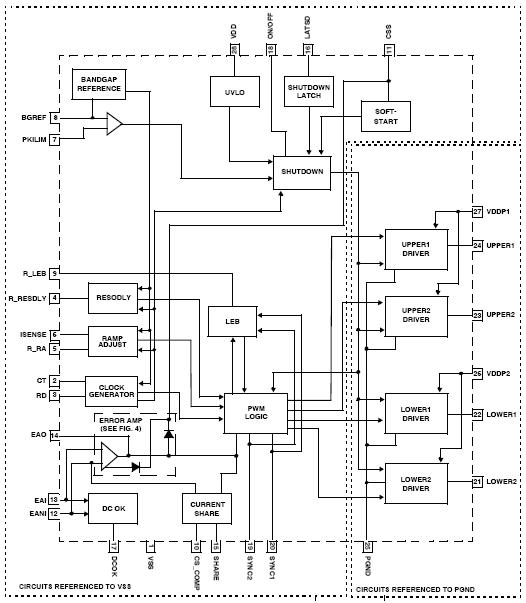

The ISL6551IREC is a zero voltage switching (ZVS) full bridge PWM controller designed for isolated power systems. This part implements a unique control algorithm for fixed frequency ZVS current mode control, yielding high efficiency with low EMI. The two lower drivers are PWM-controlled on the trailing edge and employ resonant delay while the two upper drivers are driven at a fixed 50% duty cycle.

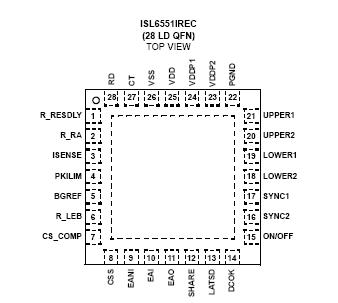

This IC integrates many features in a 28 lead 6 mm x 6 mm2 QFN package to yield a complete and sophisticated power supply solution. Control features include programmable softstart for controlled start-up, programmable resonant delay for zero voltage switching, programmable leading edge blanking to prevent false triggering of the PWM comparator due to the leading edge spike of the current ramp, adjustable ramp for slope compensation, drive signals for implementing synchronous rectification in high output current, ultra high efficiency applications, and current share support for paralleling up to 10 units, which helps achieve higher reliability and availability as well as better thermal management. Protective features include adjustable cycleby- cycle peak current limiting for overcurrent protection, fast short-circuit protection (in hiccup mode), a latching shutdown input to turn off the IC completely on output overvoltage conditions or other extreme and undesirable faults, a nonlatching enable input to accept an enable command when monitoring the input voltage and thermal condition of a converter, and VDD undervoltage lockout with hysteresis. Additionally, the ISL6551IREC includes high current highside and low-side totem-pole drivers to avoid additional external drivers for moderate gate capacitance (up to 1.6nF at 1MHz) applications, an uncommitted high bandwidth (10MHz) error amplifier for feedback loop compensation, a precision bandgap reference with ±1.5% or ±1% tolerance over recommended operating conditions, and a ±5% “in regulation” monitor.

In addition to the ISL6551IREC, other external elements such as transformers, pulse transformers, capacitors, inductors and Schottky or synchronous rectifiers are required for a complete power supply solution. A detailed 200W telecom power supply reference design using the ISL6551IREC with companion Intersil ICs, Supervisor and Monitor ISL6550 and Half-bridge Driver HIP2100, is presented in Application Note AN1002.

In addition, the ISL6551IREC can also be designed in pushpull converters using all of the features except the two upper drivers and adjustable resonant delay features.

- Full Traceability Through Assembly and Test by Date/Trace Code Assignment

- Enhanced Process Change Notification per MIL-PRF-38535

- Enhanced Obsolescence Management

- High Speed PWM (up to 1MHz) for ZVS Full Bridge Control

- Current Mode Control Compatible

- High Current High-Side and Low-Side Totem-Pole Drivers

- Adjustable Resonant Delay for ZVS

- 10MHz Error Amplifier Bandwidth

- Programmable Soft-Start

- Precision Bandgap Reference

- Latching Shutdown Input

- Non-latching Enable Input

- Adjustable Leading Edge Blanking

- Adjustable Dead Time Control

- Adjustable Ramp for Slope Compensation

- Fast Short-Circuit Protection (Hiccup Mode)

- Adjustable Cycle-by-Cycle Peak Current Limiting

- Drive Signals to Implement Synchronous Rectification

- VDD Undervoltage Lockout

- Current Share Support

- ±5% “In Regulation” Indication

- QFN Package:

- Compliant to JEDEC PUB95 MO-220 QFN - Quad Flat No Leads - Package Outline

- Near Chip Scale Package Footprint, which Improves PCB Efficiency and has a Thinner Profile